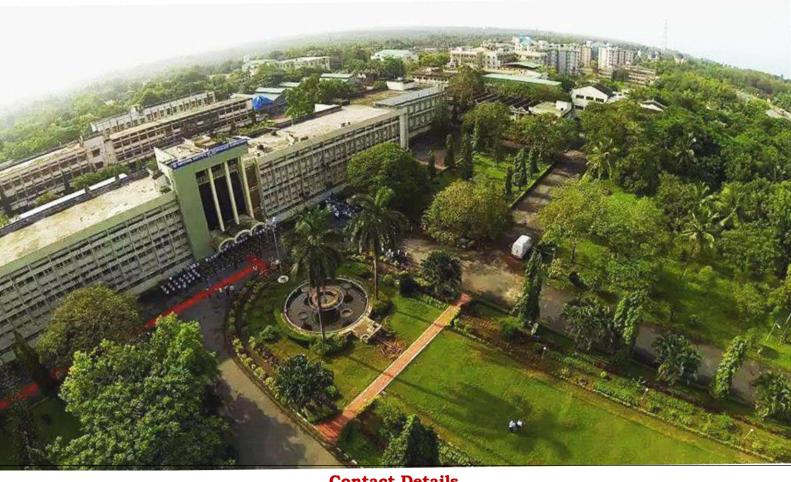

# NATIONAL INSTITUTE OF TECHNOLOGY KARNATAKA

Surathkal, Mangaluru, India 575025

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

M. Tech. In VLSI Design

# **About the Institute**

National Institute of Technology Karnataka, Surathkal is located in Mangaluru City, Karnataka State, India. The Institute was established as Karnataka Regional Engineering College (KREC) in 1960 and upgraded to the National Institute of Technology Karnataka (NITK) in 2002. The functioning of NITK is governed by NIT Act, 2007 and by the rules laid down by the Government of India from time to time. NITK Board of Governors comprises the Chairperson nominated by the Institute Visitor, the Director, and the nominated members of the Government of India, the Government of Karnataka, the NIT Council, the Institute Senate, and the nearest Indian Institute of Technology. The institute is considered as a premier centre engaged in imparting quality technological education and supporting research and development activities.

#### **Vision**

To facilitate transformation of students into good human beings, responsible citizens & competent professionals, focusing on the assimilation, generation and dissemination of knowledge.

#### Mission

- Impart quality education to meet the needs of profession and society, and achieve excellence in teaching-learning and research.

- Attract and develop talented and committed human resources, and provide an environment conducive to innovation, creativity, team-spirit and entrepreneurial leadership.

- Facilitate effective interactions among faculty and students, and foster networking with alumni, industries, institutions and other stake-holders.

- Practice and promote high standards of professional ethics, transparency and accountability.

# **About the Department**

The Department of Electronics and Communication Engineering offers an Undergraduate programme, B.Tech. in Electronics and Communication Engineering and three Postgraduate programmes, M.Tech. in VLSI Design, M.Tech. in Communication Engineering & Networks and, M.Tech. in Signal Processing & Machine Learning. In addition, it also offers M.Tech. (Research) and Ph.D. programmes in these three streams. These PG/ Ph.D. programmes have been designed to provide a platform for bright graduates and postgraduates to conduct research in state-of-the-art technologies. The Department is also a recognized centre under the Quality Improvement Program (QIP) of the Government of India. The B.Tech. in E&C engineering at NITK is one of the most sought-after programmes in the country and attracts top 1% students qualifying in the JEE(Main) exam. The M.Tech. programmes are also equally sought after by the students qualifying in GATE examination. Students graduating from the department are regularly recruited by several National and International companies working in core ECE domain, PSUs as well as Multinational companies working in VLSI, IT and Financial sectors. In recent years, many leading organizations including Texas Instruments, Intel, ARM, AMD,

Qualcomm, Broadcom, Nvidia, Cadence, Synopsys, Microchip, Tejas Networks, Samsung, ISRO, CRL etc. have recruited graduates as well as postgraduates of the department. Securing close to 100% placement of eligible undergraduate and graduate students is a regular annual occurrence. About 10% of the graduates pursue postgraduate and doctoral studies in the top-rated Universities in India and abroad. Our students have consistently secured admissions to top rated institutions in US, UK, France, Germany, Canada, Singapore, and in many other countries.

The department has been actively involved in several quality enhancement projects such as Project IMPACT, PI-SSS, EENP, UK-INDIA REC Project, TEQIP and SMD-VLSI Project during the last two decades. In recent years, the department has embarked on R&D projects funded by central agencies such as MHRD, DIT, DST, SERB, ISRO, Govt. of India and private industries. Several research projects funded by these agencies have been executed. In addition, the department is involved in rendering consultancy and advisory services to DRDO, Indian Railways, Public Sector Banks, and the district police force and the district administration of Udupi and Dakshina Kannada districts. The department has initiated and maintained a continuous dialogue with leading academic institutions, leading industries and R&D organizations. This has resulted in the department being able to develop in step with evolving expectations of students, employers and other stake holders.

#### **Vision**

To be a model for academic excellence in the area of Electronics & Communication Engineering.

#### **Mission**

- M1. Impart quality teaching-learning-experience with state-of-the-art curriculum.

- M2. Enhance Research, Consultancy and Outreach activities.

- M3. Increase the visibility of academic programmes globally and attract talent at all levels.

- M4. Foster sustained interaction with the alumni, industries, R & D organizations, world class universities and other stakeholders to stay relevant in the globalized environment.

# **Programmes offered**

- 1. B.Tech. in Electronics and Communication Engineering

- 2. M.Tech. and M.Tech. (Research) in

- VLSI Design

- Communication Engineering and Networks

- Signal Processing and Machine Learning

- 3. Ph.D.

# **MTech in VLSI Design**

The postgraduate programme originally started as M.Tech. in Industrial Electronics (1968) was revised and renamed as M.Tech. in Microelectronics (2003) and later as in VLSI Design with a mandate from the Ministry of Communication & Information Technology (MCIT), Government of India with a vision to make our country a significant player in VLSI Design and related Software under its flagship Special Manpower Development Programme (SMDP). The SMD Programme, started in 1998, gave a major fillip to the M.Tech. programme by way of providing financial and administrative support for state-of-the-art hardware/software & infrastructure, faculty training, IC Chip design & fabrication, collaborative activities among the premier institutions such as IITs, IISc, NITs and some private engineering institutions in India.

#### **Admission**

Admission to the 2-year M.Tech. in VLSI Design is made in the odd semester of each session at the first-year level with Graduate Aptitude Test in Engineering (GATE) as the qualifying examination. The goals of the postgraduate program in VLSI Design are to prepare students for the challenging job assignments of current VLSI and EDA industries and to carry out advanced research in the broad areas of VLSI design and its pervasive applications. To this end, the program offers advanced courses in the core domain of Digital, Analog and Mixed Signal design, Advanced Computer Architecture, VLSI Design Automation, Data Converters, etc. In addition to these, a wide variety of elective courses are also offered to enable students to specialize in a specific area.

The programme has been designed to provide our students with a strong background in theoretical, computational and practical aspects of the discipline which can then enable them to contribute meaningfully

to the profession as technologists, R&D professionals or academics. The program allows students meaningful engagement with industry/ world class Universities by means of internships. Many students have been able to convert their internships into job placements and Ph.D. offers. Faculty members are striving hard to foster a culture of meaningful research and development work aimed at benefiting the community at large. Several R&D and consultancy projects supported by DRDO, SERB-DST, the Ministry of Electronics and Information Technology (MeitY) are being executed.

Many PG/ Ph.D. students have made exemplary contributions to the conduct of this R&D work. Our PG students have served as interns in several organizations/ laboratories of national importance such as ISRO, DRDO, SAMEER, ADE, BEL-CRL, CDAC etc. (to name a few). In addition, many PG students do their internships in leading multinational companies working in the core VLSI domain such as Texas Instruments, Intel, Qualcomm, AMD, Analog Devices, ARM, Broadcom, Nvidia, Cypress Semiconductor, Samsung, etc. Most students succeed in converting these internships into job offers.

| Intake/Strength for M.Tech in VLSI Design                                                         | 2022-23 | 2021-22 | 2020-21 | 2019-20 |

|---------------------------------------------------------------------------------------------------|---------|---------|---------|---------|

| Sanctioned Intake                                                                                 | 33      | 33      | 33      | 29      |

| Total number of students admitted in the Programme (including sponsored / self-financed students) | 38      | 37      | 33      | 29      |

# **Programme Educational Objectives (PEOs)**

- **PEO1**: Pursue a successful career in the field of VLSI Design and related fields and contribute to the profession in Industry /Research/ Academia.

- **PEO2**: Continuously learn, engage and update themselves in technical areas in the relevant fields, carry out independent research and handle constantly evolving multidisciplinary technological challenges.

- **PEO3**: Demonstrate effective communication skills and leadership qualities with ethical attitudes in a broad societal context while working in a multi / interdisciplinary setting.

# **Programme Outcomes and Programme Specific Outcomes**

The Department adopted the Programme Outcomes recommended by the NBA and specified two Programme Specific Outcomes.

# **Programme Outcomes (POs)**

- **PO1** An ability to independently carry out research/investigation and development work to solve practical problems.

- **PO2** An ability to write and present a substantial technical report/document.

- **PO3** An ability to demonstrate a degree of mastery in VLSI Design.

- **PO4** An ability to apply appropriate techniques and modern engineering tools in the design and implementation in the area of VLSI Design.

- **PO5** An ability to apply VLSI engineering and technology principles in a multidisciplinary environment through their team playing and self-learning capabilities.

# **Programme Curriculum (2022)**

The curriculum has been designed in line with the requirements of the stated POs. Further, the curriculum has various well-balanced course components under programme core, programme electives, project, and mandatory learning courses.

The mandatory learning courses include seminar and minor project. The curriculum allows students to register for a maximum of 3 credits from certified MOOC courses (NPTEL/SWAYAM etc.) for their elective credit requirement. Following is a list of courses offered for the M.Tech. VLSI Design Programme.

| Course Component                                     | Total number of credits |

|------------------------------------------------------|-------------------------|

| Program Core                                         | 26                      |

| Elective Courses                                     | 12                      |

| Mandatory Learning Courses<br>Minor Project, Seminar | 4                       |

| Major Project                                        | 12                      |

| Total (Minimum Credits to be earned)                 | 54                      |

#### Program Core (PC)

EC701 CMOS VLSI

EC702 Analog Integrated Circuit Design

EC703 VLSI Data Converters

EC704 VLSI Design Automation

EC705 IC Design Lab

EC791 Linear Algebra and Stochastic Processes

EC792 High Performance Computing Architectures

#### **Mandatory Learning Courses (MLC)**

EC727 Seminar

EC728 Minor Project

#### Project (MP)

EC729 Major Project - I

EC730 Major Project - II

#### **Electives (ELE)**

EC801 Logic Synthesis Techniques

EC802 Low Power VLSI Design

EC803 Microelectronic Devices

EC804 Digital VLSI Testing & Testability

EC805 Embedded Systems

EC806 Digital Design using FPGAs

EC807 Active Filter Design

EC808 CMOS RF Integrated Circuits

EC809 Heterogeneous and Parallel Programming

EC870 Architectures for Signal Processing and Machine Learning

#### **More Details**

To access the regulations and curriculum, please refer to the website. Scan the QR code or click the below link to access the latest curriculum.

https://qr.page/g/5qwydTFUgH9

# **Students' Performance**

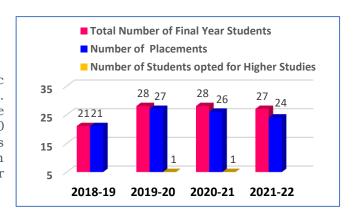

# **Students' Academic Performance, Placement and Higher Studies**

Students of the Programme have good academic performance, with an average success rate of more than 98%. During the academic years 2018-19 to 2021-22, the combined average placement & higher studies is above 90 per cent in highly reputed companies and universities abroad. The percentage of students who qualified in national/international level tests and opted to pursue higher studies is approximately 2%.

#### **Students' Publications**

#### **Journal Publications**

- 1. Naik, J.D., Gorre, P., Akuri, N.G., Kumar, S., Al-Shidaifat, A.A. and Song, H., 2022. High-Performance Graphene FET Integrated Front-End Amplifier Using Pseudo-Resistor Technique for Neuro-prosthetic Diagnosis. BioChip Journal, 16(3), pp.270-279 (IF 4.229)

- 2. Puneeth Kumar and S. Rekha, "Fast start crystal oscillator design with negative resistance control", Integration, the VLSI Journal, Elsevier Publications (SCIE, Scopus), Vol.65, pp.138-148, March 2019.

- 3. C. B. Muhammed Mansoor, Anuradha Patil, Rekha S., "1V, 20 nW true RMS to DC Convert-er based on third order dynamic translinear loop", IETE Journal of Research (Taylor & Francis), May 2022.

- 4. Samyuktha K, Santosh Kumar Sahu, Rohit Khoja, Sumit Kanu & Mandeep Singh, "Theoretical Analysis of On-Chip Vertical Hybrid Plasmonic Nanograting", Plasmonics Journal, pp. 1-7, 2021.

- 5. Samyuktha K. Reddy, & Mandeep Singh, "Nanoscale Tapered Hybrid Plasmonic Waveguide for On-Chip Silicon Photonics", Silicon, Nov., pp. 1-7, 2021.

- 6. Samyuktha k. Reddy, and M. Singh, "Porous-Silicon assisted Hybrid Plasmonic Slot Wave-guide based On-Chip Ethanol Sensor," IEEE Sensors Journal, pp. 1-7, 2022.

- 7. Puneeth Kumar and S. Rekha, "Fast start crystal oscillator design with negative resistance control", Integration, the VLSI Journal, Elsevier Publications (SCIE, Scopus), Vol.65, pp.138-148, March 2019.

- 8. Nithin, Rathnamala Rao, K. N. Bhat, Design and Fabrication of Sculptured Diaphragm Mems Low Range Pressure Sensor, Manufacturing Technology Today (CMTI Journal) Vol 19, No 10, pp.49-53, Oct 2020.

#### **Conference Publications**

- 1. Sumit Kumar, Hanumantha Rao G. and Rekha S., "A 1-V, 8.6 nA Resistor-less PTAT current reference with startup circuit", 15th IEEE India Council International Conference (INDICON), Coimbatore, India, 16-18 Dec. 2018, pp. 1-4.

- 2. Amaljith M. K., Hanumantha Rao G, and Rekha S., "Low voltage current reference circuit with low temperature coefficient", IEEE International Conference on Distributed Computing, VLSI, Electrical Circuits and Robotics (IEEE DISCOVER), 13-14 Aug. 2018.

- 3. Aparna T, Sreenivasulu Polineni and M. S. Bhat, "A Three-Stage Operational Transconductance Amplifier for Delta Sigma Modulator", IEEE International Conference on Distributed Computing, VLSI, Electrical Circuits and Robotics (IEEE DISCOVER), 13-14 Aug. 2018 -Won the Best Paper Award

- 4. Riya Raj, M. S. Bhat and Rekha S, "Library Characterization: Noise and Delay Modeling", IEEE International Conference on Distributed Computing, VLSI, Electrical Circuits and Robotics (IEEE DISCOVER), 13-14 Aug. 2018.

- 5. Harpreet Mehra and M. S. Bhat, "High Level Optimization Methodology for High Performance DSP Systems using Retiming Techniques", IEEE International Conference on Distributed Computing, VLSI, Electrical Circuits and Robotics (IEEE DISCOVER), 13-14 Aug. 2018.

- 6. Shreenivasa K, M. S. Bhat and Rekha S, "A Scheme for efficient and equitable use of public utilities through supervisory and distributed control", IEEE International Conference on Distributed Computing, VLSI, Electrical Circuits and Robotics (IEEE DISCOVER), 13-14 Aug. 2018.

- 7. Haritha G, Aparna P., Pathipati Srihari, and Gnane Swarnadh Satapathi "Analysis of real-time tracking filters implementation in FPGA", IEEE International Conference on Distributed Computing, VLSI, Electrical Circuits and Robotics (IEEE DISCOVER), 13-14 August, 2018

- 8. Anuradha Patil, Mansoor Muhammed, Hanumantha G. Rao and Rekha S., "Low power log-domain Filter", 16th IEEE India Council International Conference (INDICON2019), Marwadi Univ., Rajkot, 13-15 Dec 2019.

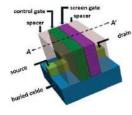

- 9. Hegde, G.R., Nikhil, K.S., Rao, R., "Simulation and Modelling of screen oxide thickness dependent implantation peak position in Silicon", Proceedings of the 6th IEEE International Conference on Electronics, Computing and Communication Technologies, IEEE CONECCT July 2020.

- 10. Mathew, S., Nithin, N., Rao, R., "Investigations on the Effect of Spacer Dielectrics on the DC Characteristics of Dual Material Gate Junctionless FinFETs", International Conference on Computational Performance Evaluation, ComPE July 2020, pp. 359-361.

- 11. Mathew, S., Nithin, Bhat, K.N., Rao, R., "Investigations on the effect of Dual Material Gate work function on DIBL and Subthreshold Swing in Junctionless FinFETs", Proceedings of the 6th IEEE International Conference on Electronics, Computing and Communication Technologies IEEE CONECCT July 2020.

- 12. Nithin, N., Rao, R., Bhat, K.N., "Impact of the diaphragm structure on the linearity and temperature sensitivity of low-pressure piezo-resistive MEMS pressure sensors", 2020 IOP Conference Series: Materials Science and Engineering 872(1), 012022.

- 13. Chinmay Malkhandi and Rathnamala Rao, "A Full-Swing, High-Speed, and High-Impedance Hybrid 1-bit Full Adder", 2nd International Conference on Computational Electronics for Wireless Communications (ICCWC-2022), June 2022.

- 14. Vinay Kushwaha, Rathnamala Rao, "High Speed Multiplexed Feedback D Flip Flop", 2nd International Conference on Computational Electronics for Wireless Communications (ICCWC-2022), June 2022.

- 15. Subham Roy, Kiran Kumar H. Lad, Rekha S., Laxminidhi Tonse, "A low mismatch current steering charge pump for high-speed PLL", 2nd International Conference on Computational Electronics for Wireless Communications (ICCWC-2022), June 2022. **Won the best paper award**

- 16. Vaishnavi Surve, Sandeep Kumar, Pradeep Gorre "High Efficiency Broadband Mixed Mode Power Amplifier for Patient Monitoring" 7th International Conference on Signal Processing and Communication (ICSC), pp. 325-329, 2021.

- 17. Naik, J.D., Gorre, P., Kumar, R., Kumar, S., Song, H. "A 73% PAE, Highly Gain Inverse Class-F Power Amplifier for S-Band Applications". In: Agrawal, R., Kishore Singh, C., Goyal, A. (eds) Advances in Smart Communication and Imaging Systems. Lecture Notes in Electrical Engineering, vol 721, Pages 467-474, Springer, Singapore (2021)

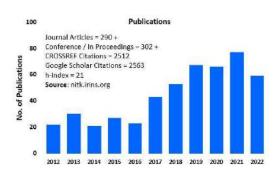

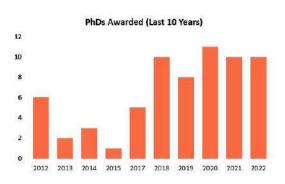

### **Publications and PhDs Awarded by the Department**

#### **Current Research Areas**

- ASIC and FPGA based System Design

- Novel Architectures for VLSI Data Converters

- Reconfigurable Architectures

- Hardware Accelerators

- Continuous-Time and Switched Capacitor Filters

- Nano-Scale Devices

- Semiconductor Device Modelling

- Compact Modelling of Devices

- RF Circuit Modelling & Optimization

- mm Wave Integrated Circuits

- Growth And Characterization of Semiconductor Thin Films

- Semiconductor Light Emitters and Photovoltaic Devices

- Smart Antennas

- Silicon Photonics and Optical Sensors

- Hardware Solutions for Image and Video Coding and Embedded Systems

- Detection And Prevention of Hardware Trojans in Processors/IPs

# **Faculty Information**

### **Associated Faculty members**

| Faculty Name            | Highest Degree             | Designation            | Specialisation                                                                                                    |

|-------------------------|----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------|

| Dr. Aparna P.           | PhD<br>(NITK, Surathkal)   | Assistant<br>Professor | Signal Processing, Image & Speech Processing, Multimedia<br>Compression                                           |

| Dr. Kalpana G. Bhat     | PhD<br>(NITK, Surathkal)   | Assistant<br>Professor | Analog and Mixed Signal VLSI Design                                                                               |

| Dr. Krishnamoorthy K.   | PhD<br>(IIT Bombay)        | Assistant<br>Professor | RF IC Design, Microwave Circuits & Measurements, Signal Processing                                                |

| Dr. Laxminidhi T.       | PhD<br>(IIT Madras)        | Professor              | Analog VLSI Design, Mixed Signal Design                                                                           |

| Dr. M. S. Bhat          | PhD<br>(IISc, Bangalore)   | Professor<br>(HAG)     | Analog & Mixed Signal Design, Submicron Devices, RF-MEMS, High-Speed Interconnects, Signal Processing             |

| Dr. Mandeep Singh       | PhD<br>(IIT, Roorkee)      | Assistant<br>Professor | Silicon Photonics and Optical Sensors                                                                             |

| Dr. Nikhil K. S         | PhD<br>(IIT Madras)        | Assistant<br>Professor | Semiconductor Device Modelling, Compact Modelling of Devices                                                      |

| Dr. Pathipati Srihari   | PhD (Andhra<br>University) | Assistant<br>Professor | Radar Signal Processing, Radar Target tracking and<br>Navigational Systems                                        |

| Dr. Prashantha Kumar H. | PhD<br>(NITK, Surathkal)   | Assistant<br>Professor | Error Control Coding, Signal Processing for Communication, RF Receiver Design                                     |

| Dr. Ramesh Kini M.      | PhD<br>(NITK, Surathkal)   | Associate<br>Professor | Dynamically reconfigurable processor for multimedia applications                                                  |

| Dr. Rathnamala Rao      | PhD<br>(IIT Madras)        | Assistant<br>Professor | Semiconductor device modeling, VLSI design                                                                        |

| Dr. Rekha S.            | PhD<br>(NITK, Surathkal)   | Assistant<br>Professor | Analog & Digital VLSI Design                                                                                      |

| Dr. Sandeep Kumar       | PhD<br>(IIT Dhanbad)       | Assistant<br>Professor | RF Circuit Modeling & Optimization, mm wave Integrated Circuits                                                   |

| Dr. Sumam David S.      | PhD<br>(IIT Madras)        | Professor<br>(HAG)     | Signal Processing, Multimedia Signal Processing, VLSI<br>Architecture for Signal Processing                       |

| Dr. Sushil Kumar Pandey | PhD<br>(IIT, Indore)       | Assistant<br>Professor | Growth and characterization of semiconductor thin films,<br>Semiconductor light emitters and Photovoltaic devices |

# Patents (Granted/Published)

- Omprakash, **M.S. Bhat** and **Dr. U. Shripathi Acharya**, "Alternative means for conductor based short distance signal/data transfer", Patent No. 301828 granted in October 2018.

- Omprakash N Sringeri and **Sumam David**, "Programmable Switch Network for swapping the connection between two sets of nodes", Patent No. 327002 granted in December 2019.

- Rohit Sharma, **Sandeep Kumar**, S. Ramesh, Kusum Yaday, Utpal Pandey, Vivek Kumar Srivastav and Deepa Gupta, "Methods and Systems for Monitoring a Remotely Located Renewable Energy Power Plant" Patent Application No. 202111025277 published in June 2021.

- Rohit Sharma, Vipin Sharma, **Sandeep Kumar**, Saumya Mishra and Rachit Patel, "Methods and systems for monitoring footwear and well-being of a person wearing the footwear" Patent Application No. 202111028580 published in July 2021.

- Rohit Sharma, **Sandeep Kumar**, S. Ramesh, Kusum Yaday, Utpal Pandey, Vivek Kumar and Srivastav, "Methods and Systems for Monitoring cap and well-being of a person wearing the cap A" Patent Application No. 202111032887A, published in August 2021.

- Rohit Sharma, **Sandeep Kumar**, S. Ramesh, Kusum Yaday, Utpal Pandey, Vivek Kumar and Srivastav, "Internet of Things (IOT) based Smart Stand for Utensils" Patent Application No. 202111035881A, published in September 2021.

- Sanjeev Kumar Raghuwanshi, Yadvendra Singh, Purnendu Shekhar Pandey, **Mandeep Singh**, Santosh Kumar, Azhar Shadab, Ritesh Kumar and Md Tauseef Iqbal Ansari "An IOT Monitoring System for Underground Mines using a Fiber Bragg Grating Chemical Sensor", Patent Application No. 202131051640 A, published in December 2021.

- Vipin Sharma, **Sandeep Kumar**, Krishna Pandey, Rachit Patel and Sapna Katiyar, "Assistance device for Visually and Hearing Impaired Person" Patent Application No. 202211039377 A, published in July 2022.

- Muralidhara, Rathnamala Rao, Veeresha R. K, Prasad Prabhu and Gautham S Shetty "Method and System for Measurement of Residual Stress by Drilling Deep Holes in a Weld-Joint" Patent Application No. 201941002849, Published in July 2020.

### **Books/Book Chapters**

- **Rekha S,** Contents contribution for Indian Adaptation of "Op-amps and Linear Integrated Circuits" Revised Fourth Edition by Ramakant A. Gayakwad, Pearson Publishers, 2021.

- **Prashantha Kumar H**, Contents contribution for Indian Adaptation of "Electronic Devices", Tenth Edition by Thomas L. Floyd, Pearson India, 2021.

- Amitesh Kumar, Brajendra Singh Sengar, Shalu Chaudhary, Saurabh Kumar Pandey, **Sushil Kumar Pandey**, Md Hasan Raza Ansari, "Receiver Architectures for 5G: Current Status and Future Prospects", a chapter in the book entitled "CMOS Analog IC Design for 5G and Beyond", Springer Publications, 2021.

- Vignesh R, Vipin sharma, Hanjung Song, **Sandeep Kumar**, "Techniques to Improve Gain-Bandwidth 5G ICs" a chapter in the book entitled "CMOS Analog IC Design for 5G and Beyond", Springer Publications, 2021.

- Pradeep Gorre, Rajesh Kumar, Hanjung Song, **Sandeep Kumar**, "Mm-wave CMOS power Amplifier for 5G" a chapter in the book entitled "CMOS Analog IC Design for 5G and Beyond", Springer Publications, 2021.

- **Sushil Kumar Pandey**, Vivek Garg, Nezhueyotl Izquierdo, Amitesh Kumar, "Recent Advancements in Growth and Stability of Phosphorene: Prospects for High-Performance Devices", a chapter in the book entitled "Sub-Micron Semiconductor Devices", Taylor and Francis Group, CRC Press, 2022.

### **Research and Development Activities**

The Department faculty members are actively involved in research and development works. Broad research areas of the faculty members are VLSI Design, Digital Signal Processing and Machine Learning, Communication Systems & Networking, IoT, 5G/6G Technologies, Antenna Design, MEMS Design, Wireless Communication, Error Control for Storage Systems, AI/ML Inspired Chip Design, Biomedical Circuit and Systems, RF Circuit Modeling & Optimization.

| S1.<br>No. | Project title                                                                                                                                                   | Sanctioned<br>Year (FY) | Duration | Funding<br>Agency                                               | Amount<br>(INR)<br>in lakhs                             | Project Cooridnator(s)/<br>Principal Investigator(s)                                                                                          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|-----------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Design and Development of Ultra-low<br>power CMOS IC for Wireless Neural<br>Monitoring System                                                                   | 2020-2023               | 3 Years  | International<br>Division, DST,<br>Govt of India                | 120.20<br>(India-<br>40.00<br>South<br>Korea:<br>80.20) | Dr. Sandeep Kumar Jointly<br>with Prof. Hanjung Song,<br>Centre of Nano-<br>Manufacturing, Inje<br>University, Busan, South<br>Korea          |

| 2          | Design, Development of Harmonically<br>Tuned GaN HEMT Power Amplifier Over<br>Broadband                                                                         | 2022-2024               | 2 Years  | ISRO,<br>Govt of India                                          | 14.05                                                   | Dr. Sandeep Kumar                                                                                                                             |

| 3          | Development of Highly Conductive<br>Ultrathin VS2 Crystals for High-<br>Performance Flexible Supercapacitors                                                    | 2020-2022               | 2 Years  | SERB - DST,<br>Govt of India                                    | 27.73                                                   | Dr. Sushil Kumar Pandey                                                                                                                       |

| 4          | Nanophotonic porous-silicon based<br>nanostructures for ultra-fast methanol<br>sensing at room temperature                                                      | 2022-2025               | 3 Years  | SERB-DST,<br>Govt. of India                                     | 35.59                                                   | Dr. Mandeep Singh                                                                                                                             |

| 5          | Development of low phase noise optoelectronic oscillator with phase compensation approach for radar application                                                 | 2022-2025               | 3 Years  | DRDO LRDE                                                       | 30.28                                                   | Dr. Mandeep Singh; Co-<br>PI: Prof. M. Kulkarni; Co-PI<br>at IIT (ISM) Dhanbad: Prof.<br>Sanjeev Kumar<br>Raghuwanshi;                        |

| 6          | Design and fabrication of on-chip<br>vertical hybrid plasmonic waveguide<br>based nanograting gas sensor                                                        | 2023-2026               | 3 years  | CSIR-CSIO                                                       | 30.00                                                   | Dr. Mandeep Singh                                                                                                                             |

| 7          | Design and Development of Nanoscale<br>Integrated System along with Conformal<br>Antenna as Capsule Prototype for<br>Wireless Capsule Endoscopy                 | 2021-2024               | 3 Years  | BDTD Scheme,<br>Ministry of S&T,<br>DST, Govt of<br>India       | 74.00                                                   | Dr.Sandeep Kumar along<br>with B. K. Kanaujia, JNU<br>and AIIMS New Delhi                                                                     |

| 8          | Development of design essentials for Ga2O3 based FinFET for SOC in automotive applications.                                                                     | 2020-2022               | 2 Years  | SERB-DST,<br>Govt. of India.                                    | 25.90                                                   | Dr. Nikhil K. S.                                                                                                                              |

| 9          | Programmable photonic microwave signal generation using on-chip spectral shaper for satellite communication                                                     | 2022-2024               | 2 Years  | SAC-ISRO,<br>Ahmedabad                                          | 22.51                                                   | Dr. Mandeep Singh                                                                                                                             |

| 10         | Engineering novel label free multi-layer<br>plasmonic nano-biosensor for DNA<br>hybridization                                                                   | 2020-2025               | 5 Years  | DBT, Ministry of<br>Science and<br>Technology,<br>Govt of India | 57.00                                                   | Dr. Mandeep Singh                                                                                                                             |

| 11         | Design and Development of GaN HEMT<br>Based LNA for L5 and S-Band IRNSS<br>Receiver                                                                             | 2020-2023               | 3 Years  | SERB - DST,<br>Govt of India                                    | 30.00                                                   | Dr. Sandeep Kumar                                                                                                                             |

| 12         | IMPRINT-2 project, Development of cost-effective Radiofrequency ablation system and magnetic hyperthermia equipment for thermal therapies of cancerous tumours. | 2019-2022               | 3 Years  | MHRD                                                            | 48.94                                                   | Dr. Ajay Kumar Yadav<br>Dr. PU Saxena, KMC<br>Attavar, Manipal.; Dr. B.<br>Satish Rao, MAHE;<br>Dr. U. Shripathi Acharya<br>Dr. Laxminidhi T. |

| 13 | Investigation of photonic generation of microwave arbitrary Waveform for sensing applications                                                              | 2019-2022           | 3 Years | MAHE                                   | 6.00   | Dr.Mandeep Singh                                                                                                                 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|----------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 14 | Special Manpower Development Project<br>on VLSI (SMDP-VLSI) phase-III – Chips-<br>to-Systems                                                               | 2014-2019           | 5 Years | (DIT) MCIT,<br>Govt. of India          | 160.00 | Dr. Ramesh Kini M.<br>Dr. Laxminidhi T.                                                                                          |

| 15 | Intel Embedded Initiative                                                                                                                                  | 2011-<br>continuing |         | Intel<br>Corporation                   | 5.30   | Dr. Sumam David S.<br>Dr. Ramesh Kini M.                                                                                         |

| 16 | Building capacity in teaching and collaborative research in sensor systems for public utilities—with emphasis on water and electricity distribution system | 2016-2018           | 2 Years | Royal Academy<br>of Engineering,<br>UK | 47.50  | Dr. M. B. Saidutta,<br>Dr. M. S. Bhat and<br>Dr. K. P. Vittal, jointly with<br>Univ. of Birmingham UK,<br>IBM India, RBEI India. |

### **Memorandum of Understanding**

- An agreement of cooperation (AoC) is signed between Department of Electronics and Communication of National Institute of Technology, Karnataka, India and Department of Nanoscience and Engineering / BK21PLUS Nano Convergence Project Group of INJE University, Gimhae, South Korea with a focus on Exchange of Faculty/Exchange of Research Scholars and Students/Exchange of information and materials in those fields which are of interest to both parties /Activities such as collaborative research, Lectures, and Symposiums etc/ Joint Cultural Programmes in January 2019.

- An agreement of cooperation (AoC) is signed between the Department of Electronics and Communication Engineering of National Institute of Technology Karnataka, Surathkal and Institute of Radio Frequency and Optoelectronics Integrated Circuits plus State Key Lab of Bioelectronics of Southeast University, Nanjing, Republic of China with a focus on Exchange of Faculty/Exchange of Research Scholars and Students/Exchange of information in those fields which are of interest to both parties /Activities such as collaborative research, Lectures, and Symposiums etc/ Joint Cultural Programmes in February 2019.

# **Laboratory Resources**

#### **Academic Laboratories in VLSI and Allied Areas**

- 1. VLSI Lab

- 2. IC Design Lab

- 3. Digital System Design Lab

- 4. Analog Electronics Lab

- 5. Microprocessor and Embedded Systems (MPES) Lab

- 6. Semiconductor Devices Lab

- 7. RF and Antenna Systems Lab

- 8. Applied Photonics Lab

- Analog & Sub-THz RF Integrated Circuits and Microsystems Lab

- 10. DSP Lab

# **Major Equipment / Facilities in the Department**

- Cadence Design Suite

- Synopsys EDA Tools

- Visual TCAD

- Mentor Graphics Tools

- XILINX Vivado Design Suite

- High-end Workstations, Servers, and Desktops

- FPGA boards & development tools for system design

- Chemical Vapour Deposition System

- Campus wide MATLAB License

- DSP Code development tools and evaluation kits from TI & AD

- Analog and Embedded Boards from TI

- ARM based code development tools and boards

- Intel FPGA Boards

- RF and Optic Design Hardware / Software: ADS, HFSS, SDR tools

- Vector Network Analyzers

- Spectrum Analyzer

- Digital Logic Analyzer

- PCB Prototype Machine (LPKF)

- Chemical-free Through Hole Plating System

- Microwave X band benches

- Antenna Trainers

- FSO Link Setup (Lightpoint)

- Wireless Comm Trainer Kits

- LD Driver, LD Module, PD Module, Power Meter

- Fibre Optic Power Source & kits

- Optical Fibre Trainer kits

- LD Modulator (Transmitter)

- FORX-200m (Receiver)

- Wireless digital comm. training system (Wi-CommT)

- Mixed Signal Oscilloscope

- 80MHz Function/Arbitrary Waveform Generator

- Digital Source meter with Safety universal Test Lead kit

- Microwave experiment kits

- Microcontroller Kits

- Network Simulator/ Emulator

- Systems Vue University License Bundles

- Opti-System Software

- COMSOL Multiphysics Pathology Microscopy setup

# **Department Library**

To Department has an exclusive library with about 3800 titles including text books and reference books. Students are allowed to issue two books at a time for a duration of two weeks. The books in the library have been procured with the help of research project grants awarded to the department.

### **IC DESIGN / CHIP TAPEOUT**

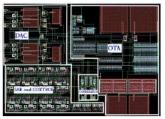

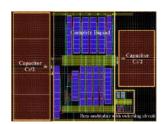

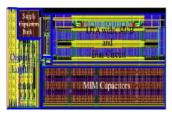

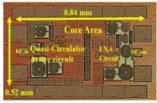

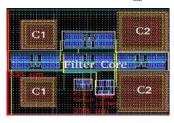

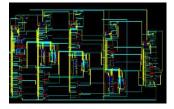

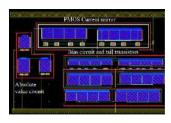

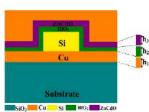

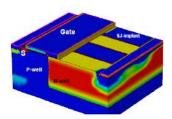

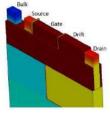

Some of the ICs designed / taped-out by the department through Europractice (IMEC Belgium), SCL Chandigarh, BEL & SITAR Bengaluru.

Flash ADC 350 nm Technology

Reconfigurable DSP Kernels & SAR ADC 180 nm Technology

Gm-C & Active –RC Continuous time filters 180 nm Technology

2-B per step SAR ADC 90 nm Technology

PLL 65 nm Technology

Non-binary SAR ADC 90 nm Technology

Class-D Amplifier 180 nm Technology

SSF Filter 180 nm Technology

10-14 B Programmable SAR/ Σ-Δ ADC 180 nm Technology

Quasi Circulator Low Noise Amplifier

GM-C Filter 65 nm Technology

Async. Hybrid Pipeline Ripple Carry Adder 180 nm Technology

RMS-DC Converter 65 nm Technology

All-optical switch using Zn-doped CdO<sub>2</sub>

Triple RESURF DeMOS

3D schematic of DeFinFET

Test Board for Gm-C & Active RC Filters

3D schematic of DMG-JLFinFET

Lattice Structure of VS<sub>2</sub> Monolayer

FinDiode

#### **RFMEMS Switches**

RFMEMS Switch 1GHz

RFMEMS Switch 5 GHz

RFMEMS Switch 2 GHz

RFMEMS switch Test Board

### **Collaboration with industry and other organizations**

The Department has ongoing interaction with many industries and academic institutions for joint R&D projects including Students Internships and Faculty exchange programs. Following are some of the industries/universities/ R&D organizations of interest.

- Anvetion Labs

- Bharat Electronics

- Cadence

- Calligo Technologies

- CoreEL Technologies

- CSIR Labs

- Emulex Communications

- Fluxgen Engg. Technology

- Google

- Infineon Technologies

- LEOS, ISRO

- MCIT, Govt. of India

- NIO Goa

- Robert Bosch

- SITAR

- Synopsys

- Texas Instruments

- Xilinx

- IISc, Bangalore

- IITB, IITG, TIFRB

- ECAM, Lyon, France

- HEIG-VD, Switzerland

- INJE University, Republic of Korea

- Michigan State University, Michigan

- Northeastern University, Boston

- Southeast University, Nanjing, China

- Univ. College Cork, Ireland

- Universita Degli Studi di Pavia, Italy

- Univ. of Southern California

- McMaster University, Canada

- Univ. of Victoria, Canada

- Univ. of Applied Sciences Western Switzerland, HEPIA, Geneva

- East China University, China

- Baylor College of Medicine, Houston

#### REMINISCENCES OF ALUMNI

This section contains accounts of the experiences of students who have graduated from the M.Tech. program.

"I enrolled in the masters of technology course in NITK in 2020. It was humbling to be reminded everyday of the vastness of the field of semiconductors and their ever-expanding innovations and discoveries. Opportunities to learn and improve ourselves were always up for grabs in the form of assignments, projects, and self-study assessments. It instilled in me a respect for the industry and curiosity in current technology and how to better it. I am presently working on verifying the performance of future-gen SoCs."

Pooja Gorle, IP Design Verification Engineer, Samsung Electronics, Bangalore, India

"The M.Tech program in VLSI Design at NITK Surathkal gave me an excellent boost in my career. The course and curriculum have been designed to meet the current semiconductor industry requirements. The faculty and infrastructure are one of the best in the country. I had the opportunity to design a circuit for High-Speed Full Adder and build an automation script to characterize it using open-source EDA tools, and this exposed me to the world of automation and the vast EDA industry. Presently, I am working as an Analog Engineer looking after the reliability improvement of Analog circuits."

Chinmay Malkhandi, EDA Engineer, Texas Instruments, Bangalore, India

"I was part of the M.Tech VLSI programme at NITK and it was an amazing journey of 2 years both personally and professionally. The curriculum which the department puts forward is always fine-tuned with the latest trends in VLSI Industry. During my course period, I have learned core concepts of CMOS VLSI design, analog circuit design, physical layout design and physical design algorithms which run in the backend of sophisticated CAD tools in the industry. I have developed a mini-CAD tool for physical design, SAR Analog to Digital Converter and also completed various FPGA projects, during the course of the programme. As part of the VLSI campus recruitment programme, I got the opportunity to work as an intern in Intel's physical design team on Improving efficiency of Design Planning for top-down IP implementation. Campus placements for the VLSI stream

are exceptionally good and I am delighted to see all the students being placed in some of the top rated MNCs. I am a proud alumnus of this programme and currently working as a lead of front-end design verification team for a future chip in Qualcomm. Thank you NITK VLSI Department for all the great opportunities."

Deepak Mohan, SoC DV Engineer, Qualcomm, Bangalore, India

#### **Contact Details**

Head of the Department, Department of Electronics and Communication Engineering National Institute of Technology Karnataka, Surathkal Srinivasnagar, Mangaluru - 575025, India

Tel.: +91 824 247 3046, +91 824 247 4055 Fax. +91 824 247 4033 Email: hodece@nitk.edu.in Website: www.ece.nitk.ac.in